Products & Technologies

Products & Services

Contact

Back to Menu

Products & Services

Products & Technologies

Services

Resources

Contact

Allowing a Direct Connection Between Chips or Wafers

Heterogeneous integration helps semiconductor companies combine chiplets based on a variety of functions, technology nodes and sizes in advanced packages, enabling the combination to perform as a single product. The need for transistors in applications like high-performance computing and artificial intelligence continues to increase at an exponential rate, while the ability to shrink transistors with classic 2D scaling is slowing and becoming more expensive—heterogeneous integration solves this industry challenge. It is a core component of a new playbook that enables chipmakers improve chip performance, power, area, cost and time to market (PPACt) in new ways.

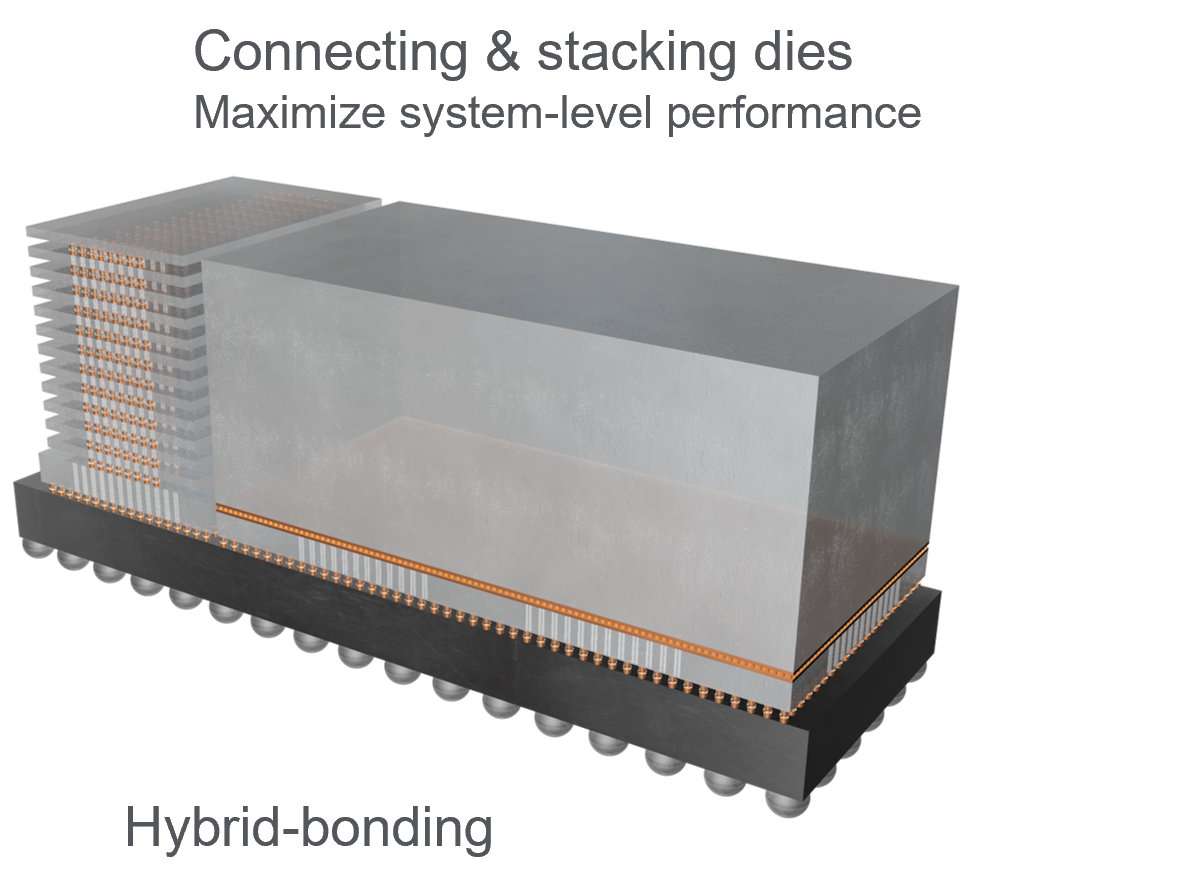

Chip makers might integrate chiplets into advanced 2.5D and 3D packages using through-silicon vias (TSVs) and/or hybrid bonding. Through-silicon vias allow designers to increase performance and reduce power consumption significantly, compared to the legacy chip on PCB approach. The latest packaging innovation, hybrid bonding, allows a direct connection between chips or wafers. Compared to TSVs, hybrid bonding will enable further increase in performance and reduce power consumption further. In hybrid bonding, die are stacked one on top of the other, and extremely fine pitch copper-to-copper interconnect is used to provide the connection between these die.

Copper-to-copper hybrid bonding enables performance that is very close to monolithic designs, with almost no power and signal penalties. The technology challenge is achieving defect-free copper-to-copper bonding with almost zero die-to-die alignment errors, all at a lower cost. This requires major modification of upstream and downstream processes as well as device design. Integrated process development and co-optimization play a critical role here.

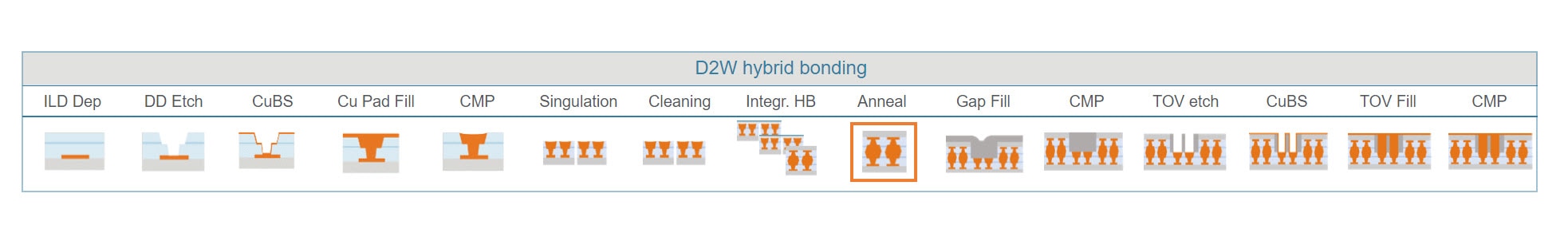

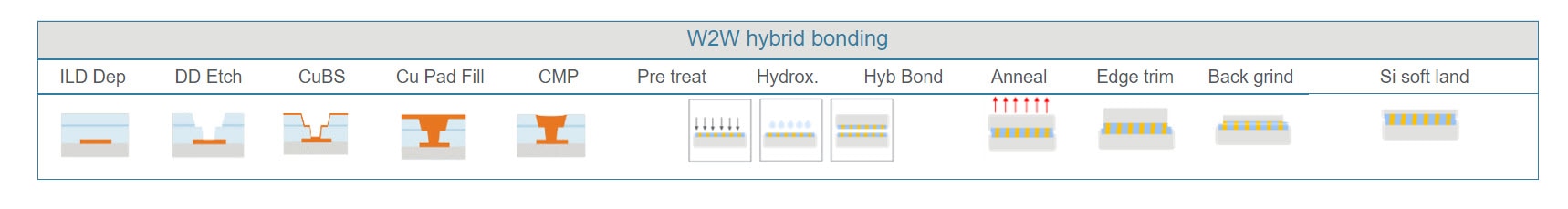

Applied Materials has a diverse set of technologies and solutions including dielectrics deposition, metals deposition, electroplating, chemical mechanical planarization (CMP) and etch to support various stages of the hybrid bonding process flow. Applied Materials’ Insepra™ SiCN and Catalyst CMP systems enable state-of-the-art hybrid bonding with new materials and enhanced surface preparation.

We also collaborate with development partners to provide our customers with the technologies to develop and ramp complete end-to-end hybrid bonding solutions.

The first collaboration is wafer-to-wafer, used in CIS and NAND and of potential interest for DRAM. Applied is working with EVG to develop an integrated process for wafer-to-wafer hybrid bonding.

The second is die-to-wafer hybrid bonding where chiplets are bonded one at a time. This process variation is of interest for logic and High-bandwidth memory (HBM) DRAM. To achieve this, we are collaborating with Besi, the leader in pick-and-place and bonding technology.

More information on hybrid bonding can be found on our Master Class and blogs on this topic.